Power Management in Embedded Systems

NOTE: This article/blog is Copyright TronicsZone. It cannot be reproduced without prior written approval.

Introduction

The modern electronic devices are constantly in search of more efficiency in all aspects. One of the most important criteria that enhances the value of a device is the amount of power consumed by it. With device manufacturers moving towards an environmentally friendly green computing and clean energy concepts, it becomes imperative to design circuits that are power efficient. For example, a standalone battery-powered device such as a smartphone, one of the key factor that a customer will explore before buying will be battery life. Hence power management while designing an embedded system is essential to utilize the available power efficiently.

Classification of Embedded Systems based on Power

Almost all our day-to-day electrical and electronic devices are designed using embedded systems. An embedded system usually comprises of a microcontroller such as ARM, also FPGAs, microprocessors, ASICs and Digital Signal processors along with memory and input and output peripherals. Embedded-system based devices are efficient in multitasking, and are also capable of interfacing with the other networks and devices.

Based on the type of power consumption embedded systems are classified into two types. Portable and Non-portable. Portable devices depend on inbuilt battery for power. They can be charged and can be used on the go. Some examples of portable systems are digital cameras, handheld GPS systems, mobile phones etc. Lithium-ion batteries are the preferred in recent devices due to a highly robust charge discharge cycle. Nonportable devices require continuous connection to a source of power. More than the non-portable systems, portable systems are the primary areas of concern, where power management is essential.

Need for Power Optimization

Size and Life of battery

With miniaturization of devices and the emergence of Nano-technology, the space that a device can allot for a battery is reducing. The device is expected to efficiently utilize the available power and function without any trade-off in performance. Life of the battery comes in as an advantage during the commercialization of a device.

Performance and Power Utilization

Embedded Systems are the crux of current technology and hence more functionalities added to the existing systems every day. Hence it becomes crucial to manage power. User usage of a device is of an unpredictable nature and hence the devices are designed to meet all types of workloads.

Adaptation of Green Technologies

Power for future of electronic devices are likely to be obtained from greener technologies such as solar power. Solar power though, ecologically sustainable lacks the same power density as normal power. In such cases, devices are expected to work efficiently given any situation. Further power lost as heat has to be minimized.

Power Management Techniques

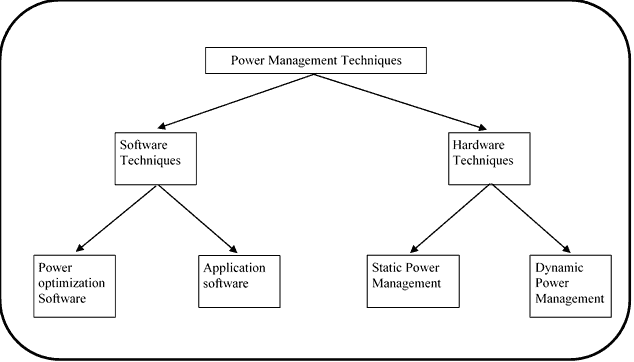

Power management in embedded systems can be done in different stages using different techniques. A compilation of available techniques is given below.

Software Power Management

Software power management techniques are applicable during the design stage and during runtime. Three steps are followed before initiating the physical design of an embedded system. They are power measurement, power analysis, and power management. Software power measurement is done as simulation at various levels of abstraction such as circuit, logic gate, RTL, or system level. Software simulations, though does not provide the real-time actual values, will give the designer an estimate based on which, the designer can optimize his design.

Power analysis is an experimentation and estimation technique to evaluate power and validate the power consumption in a system. Software such as PowerScope, PSIM are utilized to model the power consumption of the various components in the embedded system. Results of power measurement and analysis can help the designer to zero in on the idea of where power is lost and how can it be minimized. This will lead to the implementation of power management protocols.

Runtime software power optimization is done through the choice of operating system. Every OS has different methods of scheduling and performing tasks. Algorithms vary with the OS. So the designer has the freedom of choosing an OS that suits his performance requirements and at the same time reduces the power consumption. This method of power optimization leveraging the operating system is known as task based software power management.

Power Management during Physical Design

Hardware power management is of two types Static Power Management and Dynamic Power Management. Power management done during the design stage are Static Power Management (SPM) techniques. They target both hardware and software optimization. Dynamic techniques use runtime behavioural changes to reduce the power consumed in the system.

Static or design stage power management is both hardware and software. Hardware optimization relies on architectural changes, power component placement, routing, and providing proper grounding. Software optimization relies on synthesis and compilation for low power, applied at design time.

Run-Time Power Management

Run-time power management is critical in improving the efficiency of a system. Run-time techniques are termed as dynamic power management techniques. The most important techniques are Dynamic Voltage and Frequency Scaling, low-power states, power policies.

Dynamic Voltage and Frequency scaling

Dynamic voltage and frequency scaling technique has been developed for a variable voltage and frequency processor, where the frequency and the voltage of the processor are dynamically varied depending upon the workload of the processor. During idle time the voltage supplied to various components of the system are dynamically reduced so as to reduce the overall system power dissipation. Utmost care should be given to the clock design to maintain the computation time even when there is a change in voltage.

Low-Power States

Two main low-power states are suspend/resume and CPU idle (Hibernate). Suspend and resume state puts the CPU on hold and stops all ongoing processes. This state is similar to system interrupt, but the only difference is CPU is not utilized or it remains held up in the last known position.

System idle or hibernate state the CPU will have nothing to run. Only the cache works and the CPU executes power saving halt instructions, enters NAP mode which consumes less than 10mW power. The CPU disable the timers also. Thus system-idle is more power efficient than suspend-resume.

Power scheduling policies such as Greedy – Always on; Time-out – shutting down a component after a fixed inactive time; and Predictive – where a predicted time determines the switching of the components to the low power state, shall be implemented to ensure power optimization.

Conclusion

The successful design and evaluation of an embedded system requires proper power management. In the current power crunched scenario it is essential to design robust power-optimized systems to meet the workload and performance requirements of the systems. To achieve this goal, power optimization at all levels of design has to be done which is the norm here at Tronics Zone.

NOTE: This article/blog is Copyright TronicsZone. It cannot be reproduced without prior written approval.

TronicsZone

TronicsZone TronicsZone

TronicsZone